ucas-计算机体系结构-复习上

当初选这门课,就是想打牢计算机基础,没想着真要造CPU…课程确实是有点难度的,所以对于这次期末考试,我的计划是,着重复习重点的知识以及目前和可预见的将来对自己比较重要的章节,至少保证及格!! 然后学到一点东西!

必考题型复习

https://blog.csdn.net/qq_43840665/article/details/122281422

https://f.daixianiu.cn/csdn/4209862890104209.html

本科教材《》

可以做做本科后面的那个习题

第一二章

考点: 性能、成本、功耗的计算

性能:根据指令算IPC,两台机器比较性能,那个多长时间执行了多少指令

成本:硅片成本

功耗:静态功耗、动态功耗

习题1: 性能计算

在3台不同指令系统的计算机上运行同一程序P时,A机需要执行 1.0 * 10^8 条指令,B机需要执行 2.0 * 10^8 条指令,C机需要执行4.0 * 10^8条指令,但实际执行时间都是10s。请分别计算这3台机器在运行程序P时的实际速度,以MIPS为单位。这3台计算机在运行程序P时,哪一台性能最高?为什么?

解答:

1 | 常用指标MIPS(Million Instructions Per Second),每秒钟执行多少条指令. 所以每个数除10s,并且再除10的6次方(百万) |

基础知识:

MIPS并不是很合理,因为没有说明一条指令能干多少事.目前常用的一个性能指标还有MFLOPS,它是指每秒钟做多少个浮点运算.也可能会考,这个指标也有类似的问题,没衡量能做多少事.

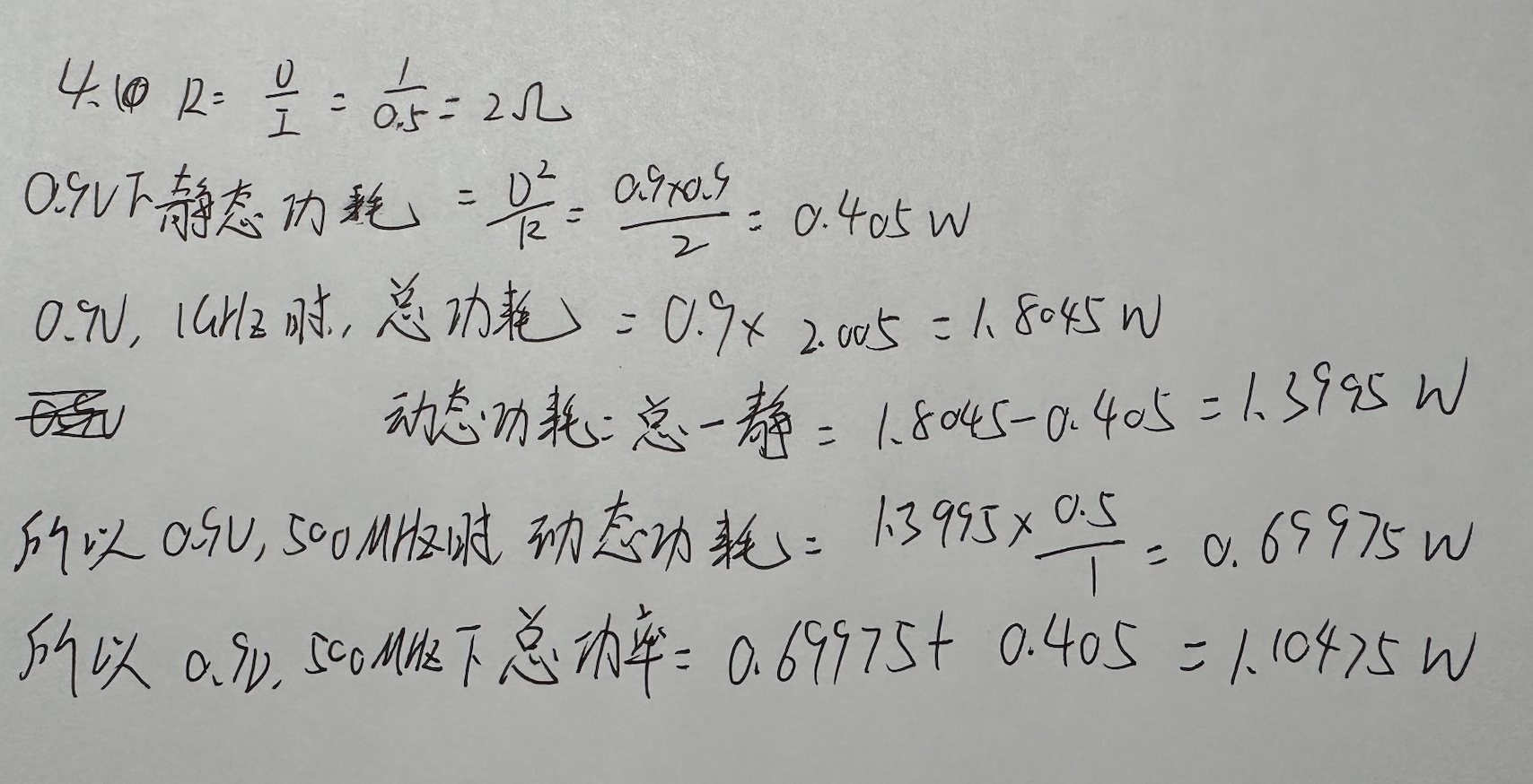

习题5: 功耗计算

对某处理器进行功耗测试,得到如下数据:时钟不翻转,电压1.05V时,电流为500mA;时钟频率为1GHz,电压1.1V时,电流为2500mA。请计算在1.1V下,此处理器的静态功耗以及500MHz下的总功耗。

基础知识:

总功耗 = 动态功耗+ 静态功耗

动态功耗与时钟频率(翻转率)成正比

解答:

先在时钟不翻转时计算电阻, R = U/I, R=2.1欧姆. 静态功耗是不变的,此时可以计算静态功耗,静态功耗 = U*U / R = 1.1 * 1.1 / 2.1 = 0.576w

我们此时计算出1.1v,1GHz下的动态功耗,然后进行比例计算,就可以得到500MHz下的动态功耗了,

1.1v,1GHz下的动态功耗 = 总功耗 - 静态功耗 = U * I - 静态功耗 = 1.1 * 2.5 - 0.576 = 2.174w

所以500MHz下的动态功耗 = 500/1000 * 2.174 = 1.087 w

所以500MHz下的总功耗 = 动态功耗 + 静态功耗 = 1.087 + 0.576 = 1.663w

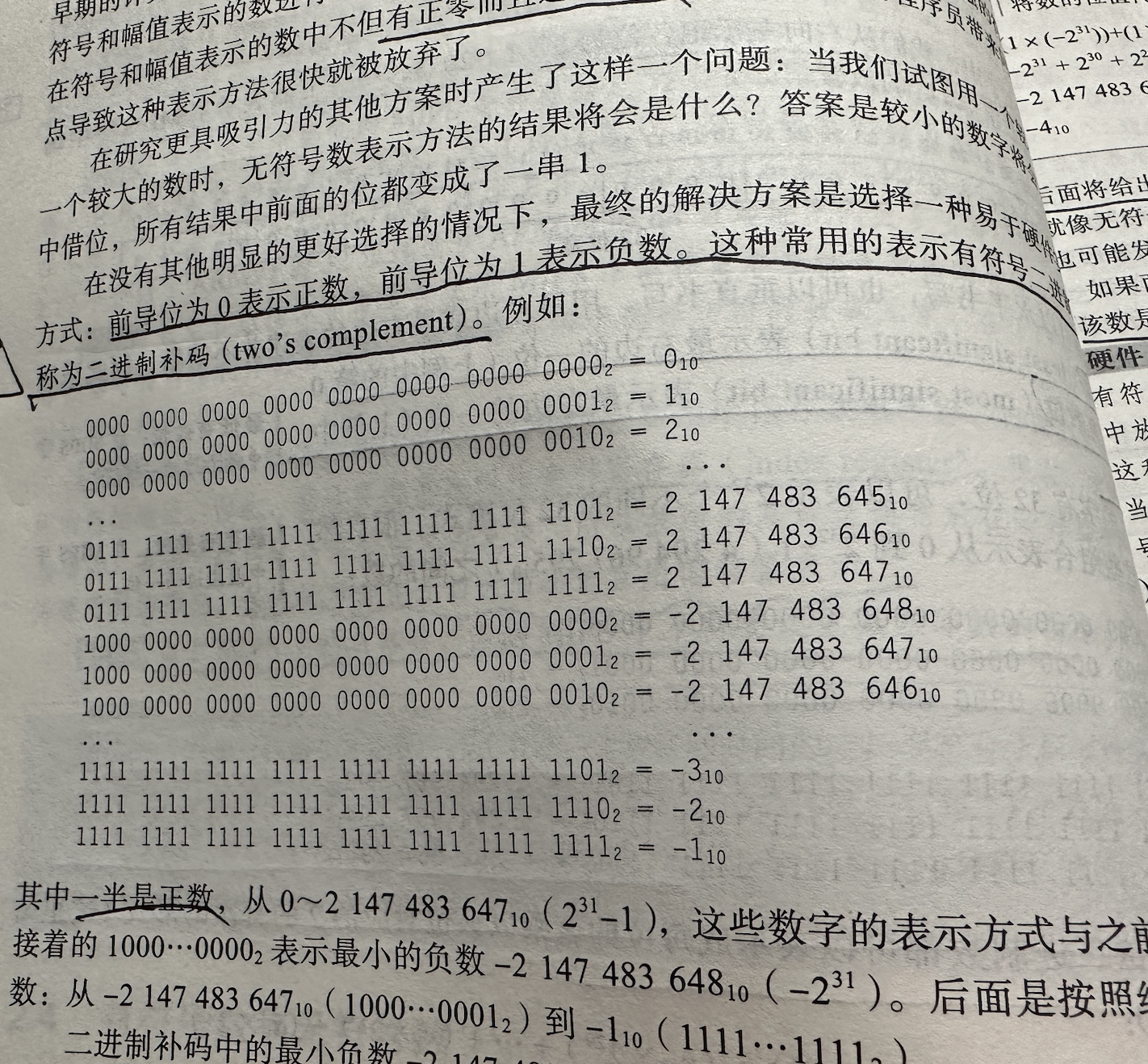

第三章 二进制与逻辑电路

浮点数的表示不考,但是定点数的要考

习题1:定点数的表示

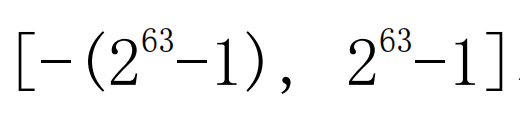

(1)分别给出64位定点原码和补码表示的数的范围

原码: 最高位符号位 0正 1负

正: 0~ 2的63次方-1

负: -(2的63次方-1) ~0

综上,

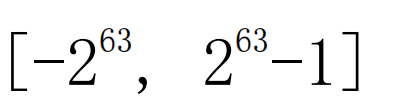

补码:

正:0~ 2的63次方-1

负:-2的63次方 ~ -1

综上

(2)在32位定点补码表示中,0x80000000表什么数

1000 0000 0000 0000 0000 0000 0000 0000

这个是补码,转换成原码后再算,

最高位不变,其余转换,然后最低位+1, 于是得到 32个0和最高位的1,溢出了??????????????

所以答案是-2的31次方

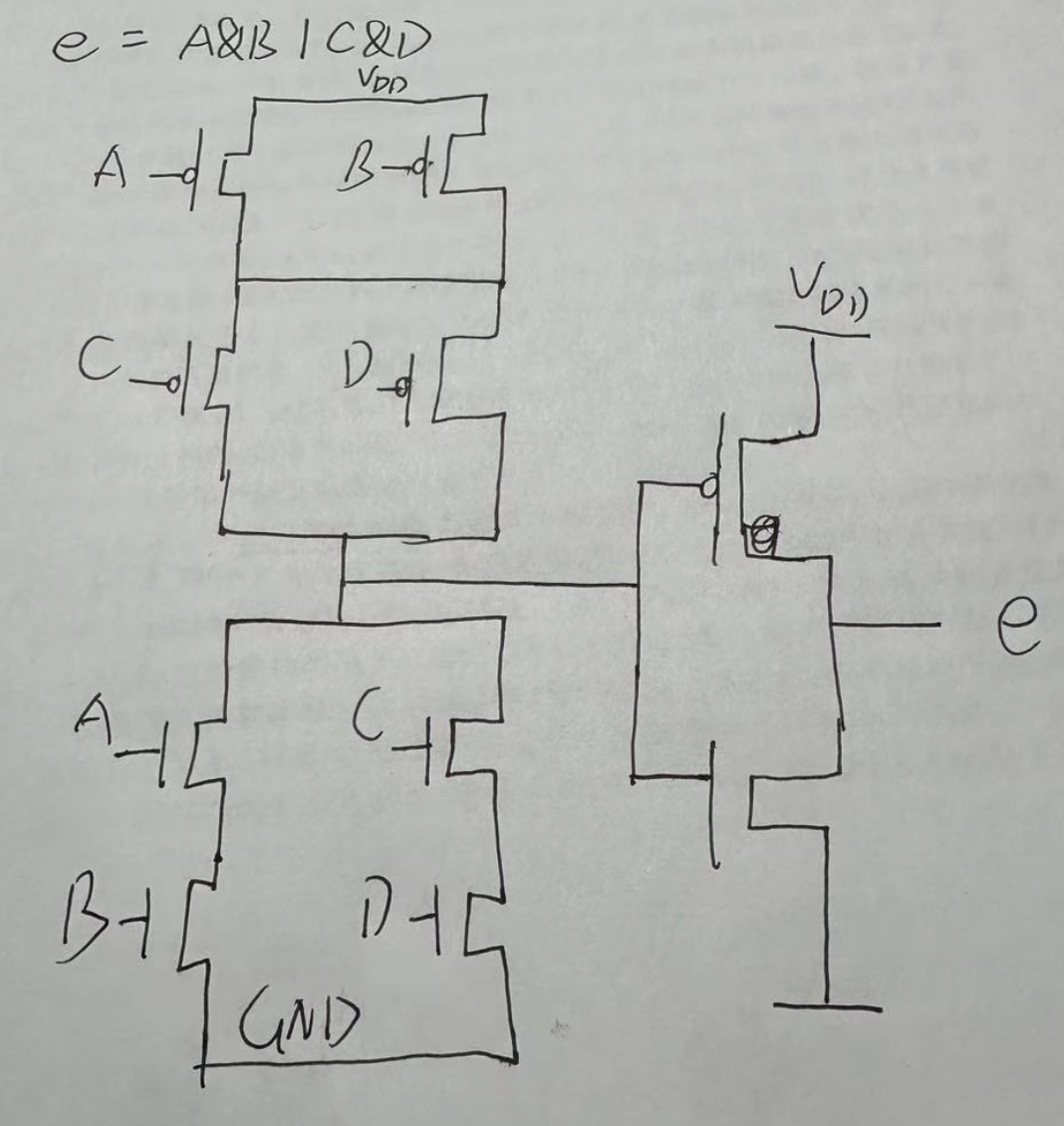

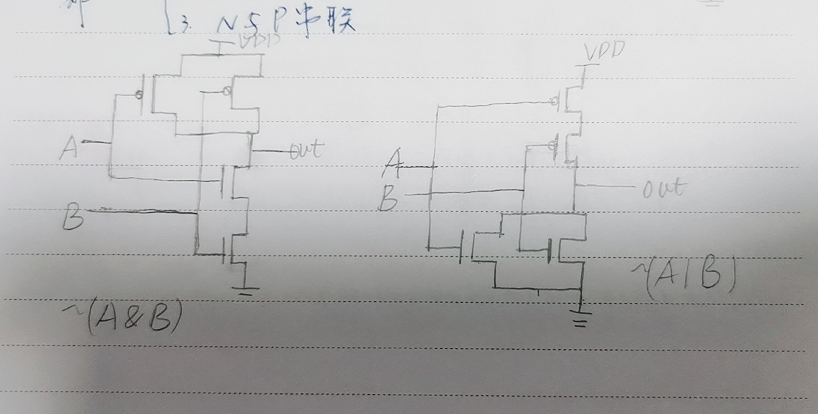

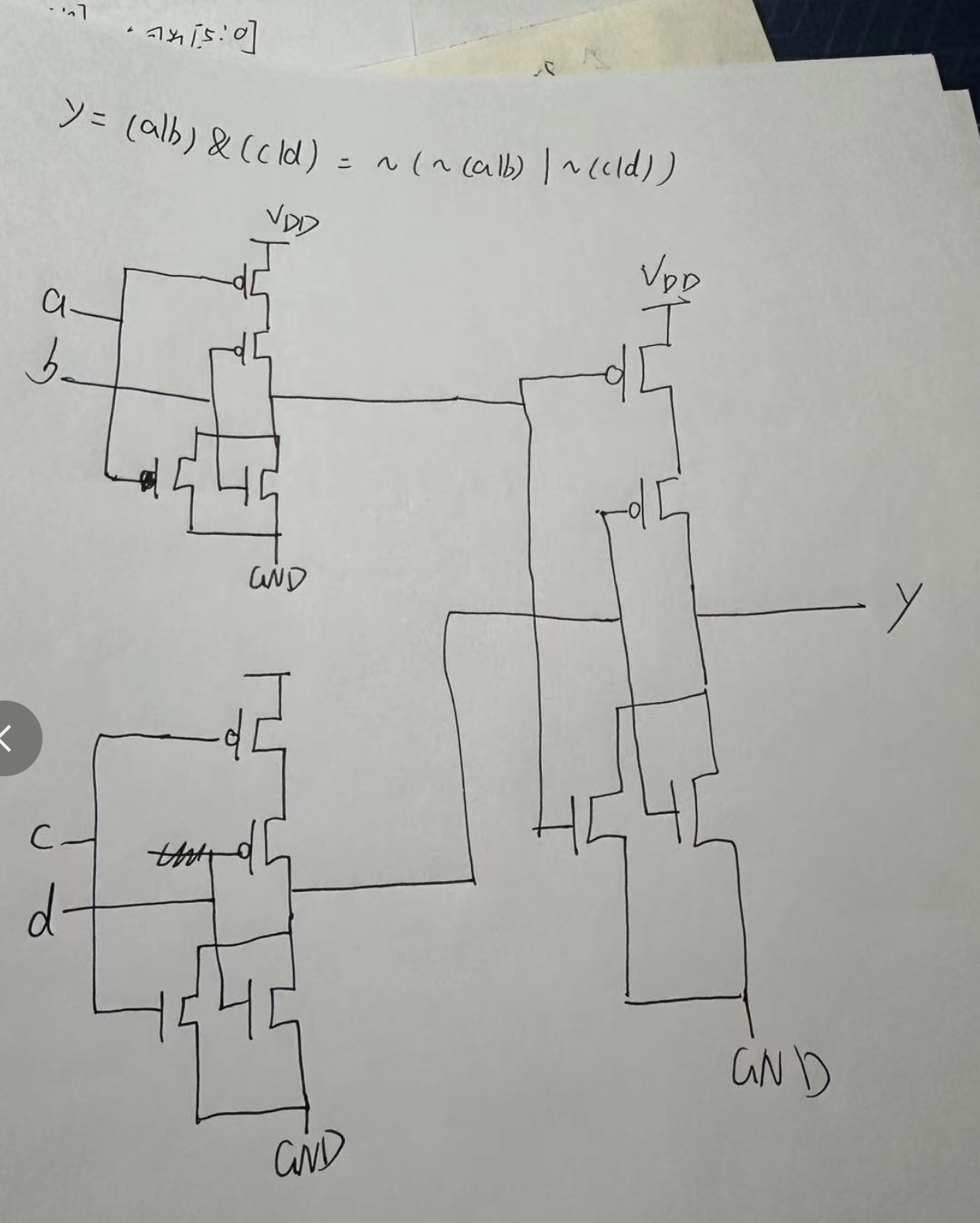

习题三:画出 e=a&b | c&d 的晶体管级电路图

本科教材p184

解法1:

首先由N管组成“正逻辑”,串联表示与,并联表示或. 再用P管组成“反逻辑”,串联表示或,并联表示与.最后再把正反逻辑串联

这得到的是 ~(a&b | c&d ), 可以加一个反相器,

解法2:

先做一个转换,转换成两级与非门的逻辑,然后再画,与非门什么的参考本科教材, 转换的话,记住那些转换公式

e=a&b | c&d = ((A&B) & ~(C&D))

还是这个做法:首先由N管组成“正逻辑”,串联表示与,并联表示或. 再用P管组成“反逻辑”,串联表示或,并联表示与.最后再把正反逻辑串联

分别8⃣️

习题四: 计算一个FO4的延迟,假设反相器的输入电容位0.0036pF,平均每个负载连线电容位0.0044pF,翻转延迟位0.023ns,每pF延迟为4.5ns

课本p48

FO4延迟 = 本征延迟(本身延迟) + 负载延迟 = 0.023 + 4.5((0.0036+0.0044)*4) = 0.167ns

负载延迟又和该电源的负载相关

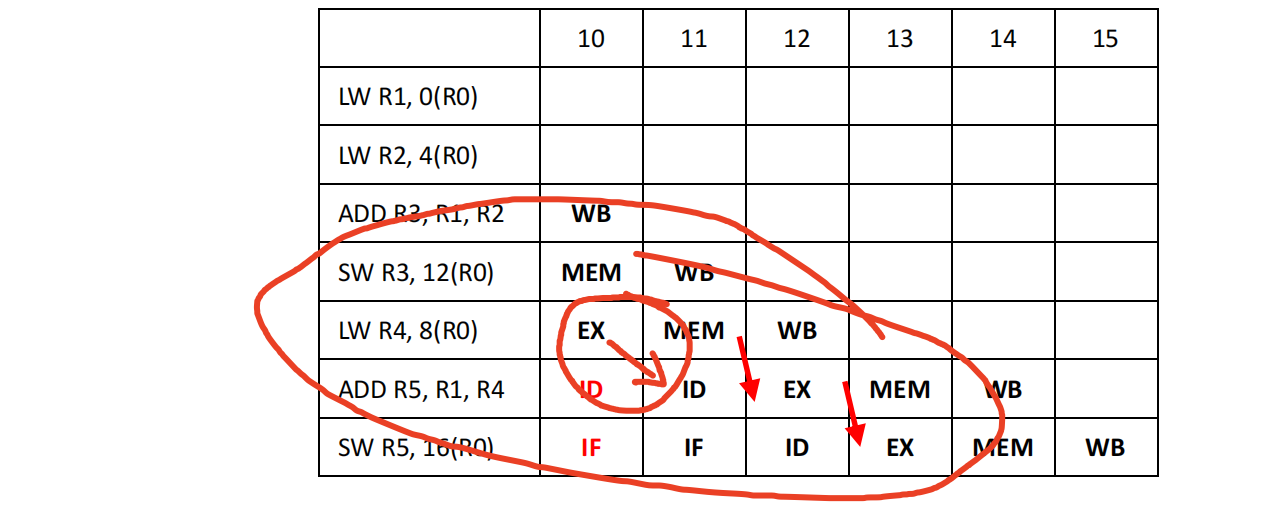

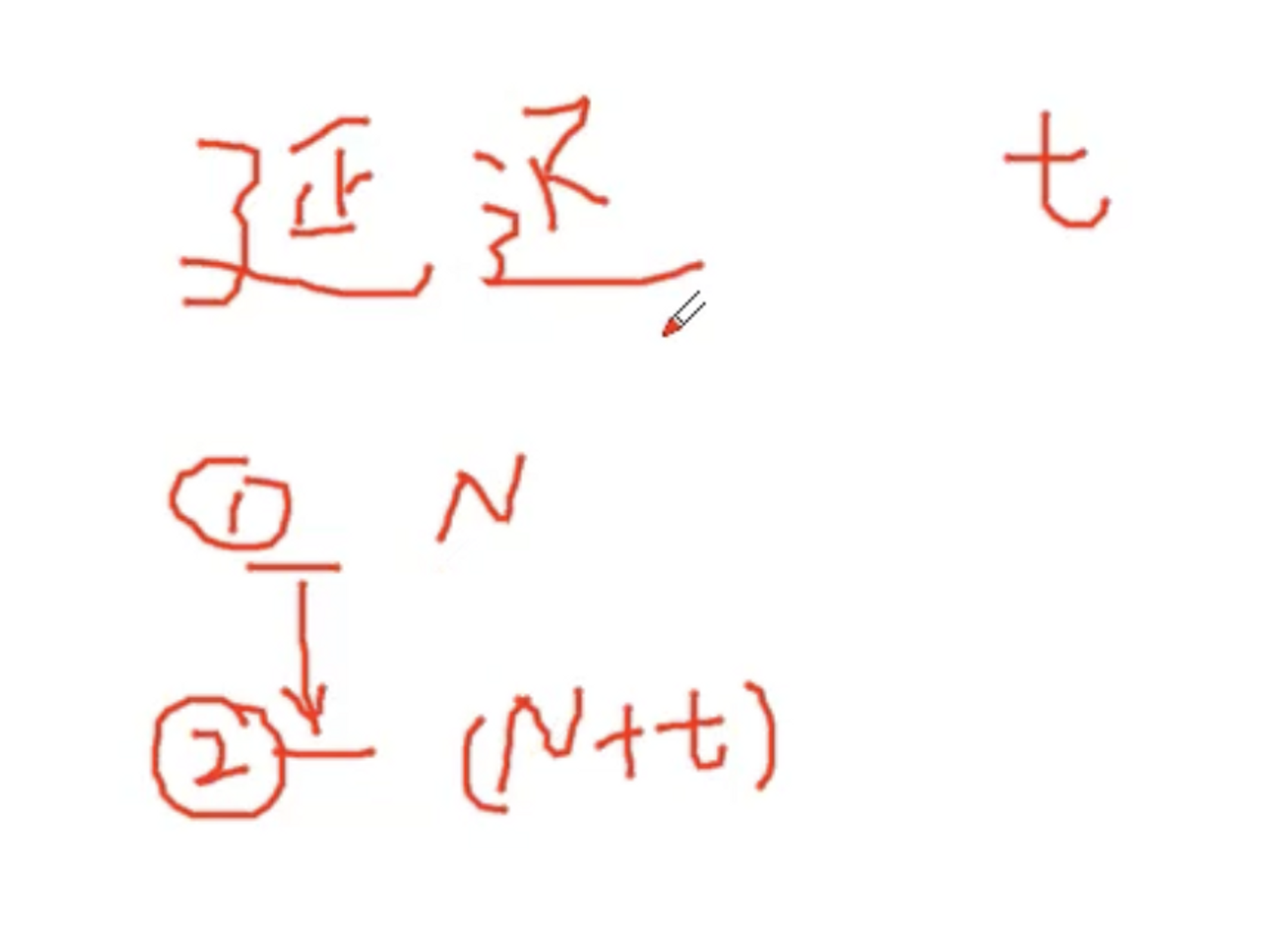

第五章 静态流水线

哪个是真相关,哪个是假相关?

五级流水的时空图,前递 ,有无前递(旁路)

给几条指令,有无前递的 画出来

和转移相关的就比较复杂了,

这里不能够前递是因为取址loadword指令的话需要访存阶段才能够拿到数值吧

空操作指令 nop的作用

空操作指令(nop 指令),其不改变程序可见寄存器、状态寄存器以及内存的状态,以及用于等待需要一定周期执行的操作。nop 指令的作用,常见的有:取指的强制访存对齐(memory alignment),防止相关风险(hazard),以及用于填充延迟槽(branch delay slot)。

第六章

执行延迟:统一到这个

mips 转移指令有延迟槽??

https://blog.csdn.net/weixin_43752162/article/details/122136323

前递(旁路)有哪几种?

mem -》 ex

ex -〉 ex

啥叫全旁路??

load的时候需要在mem才能给前递??

mips寄存器

第七章 多发射

第八章 转移预测

今年大概率考那个预测情况,推演?看ppt

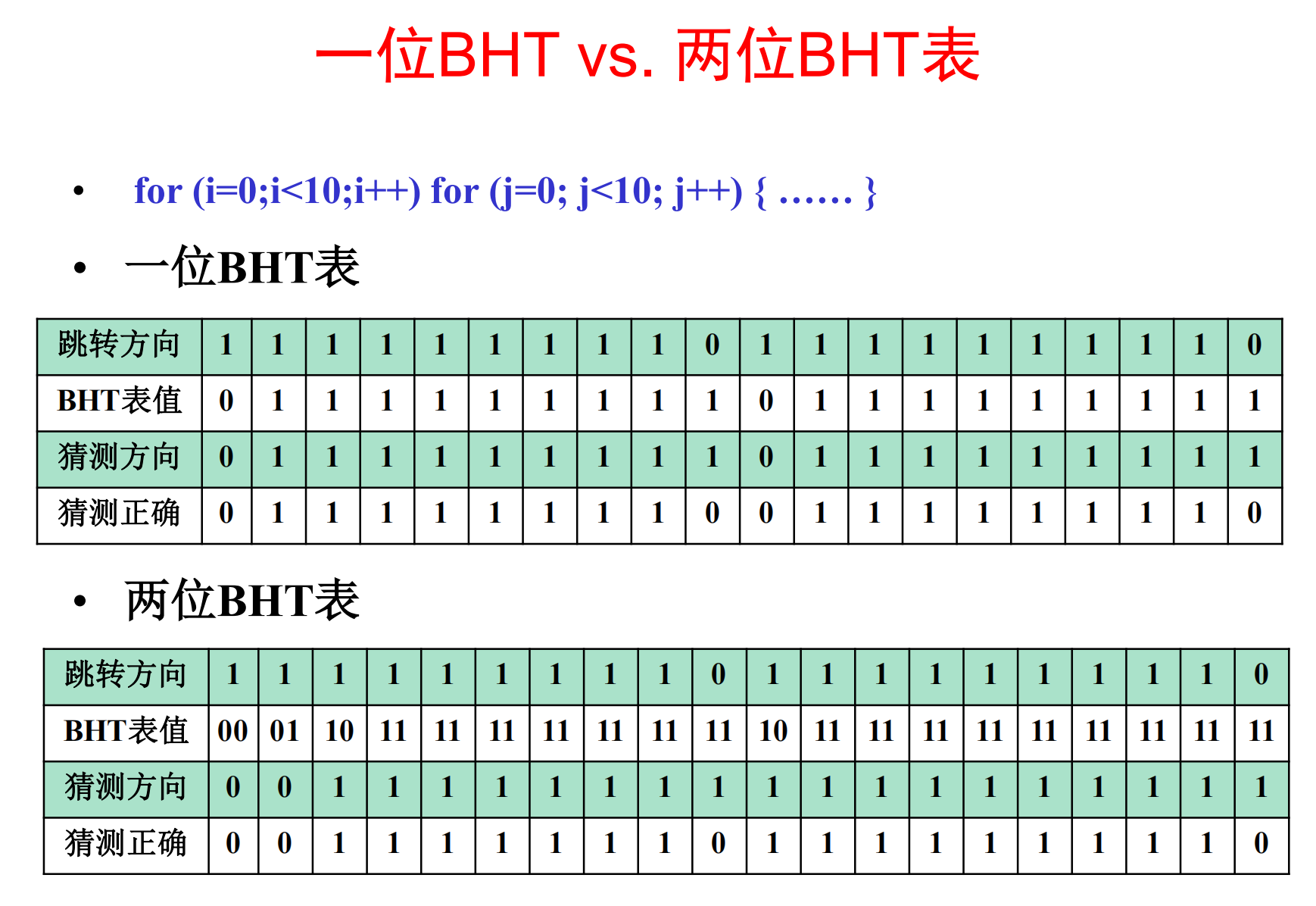

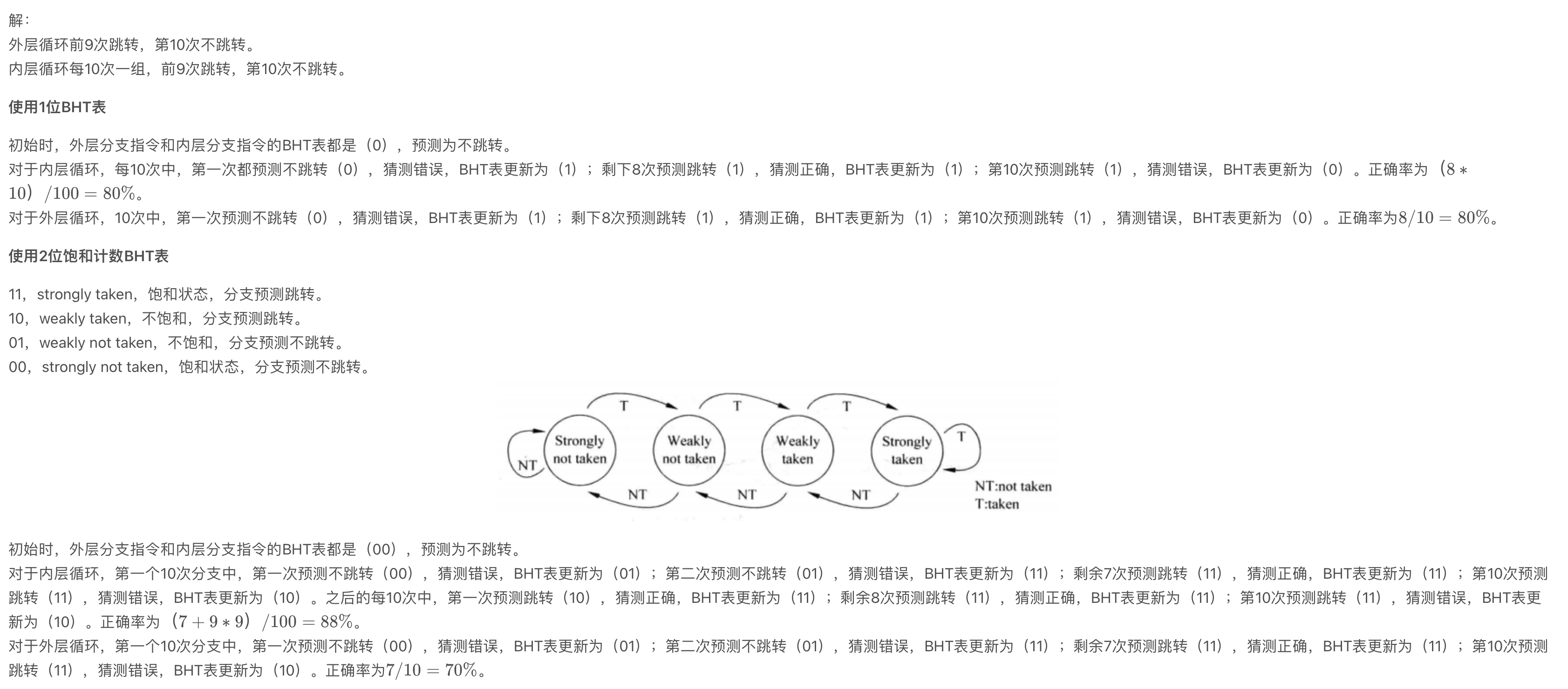

分析:for (i=0;i<10;i++) for(j=0;j<10;j++){…}的分支预测正确率。(2021复习题)

分析:for (i=0;i<10;i++) for(j=0;j<10;j++) for(k=0;k<10;k++){…}的分支预测正确率。(2021真题)

(7+999)/1000,(7+99)/100,7/10?

for(R3=9;R3>0;R3–)for(R2=9;R2>0;R2–)for(R1=9;R1>0;R1–){…}

R0的值恒为0

BENZ,BEQZ均为条件分支指令;

BENZ R1,NAME;//R1不等于0,程序跳转,以NAME为偏移地址

BEQZ R1,NAME;//R1=0,程序跳转到,以NAME为偏移地址

否则,执行下一条指令

**bne (不相等则分支):**bne $s0,$s1,L1

第九章 运算部件

华莱士树

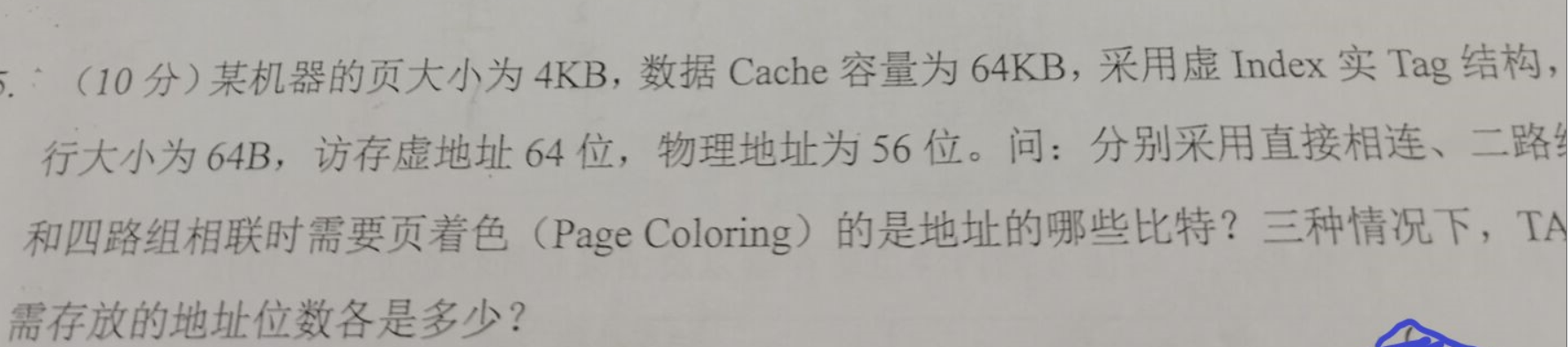

第十章: 高速缓存

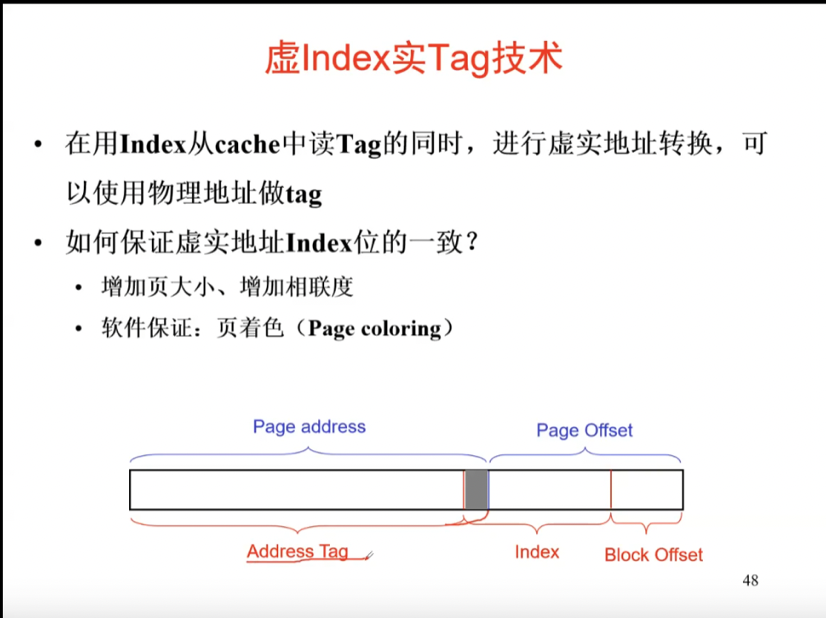

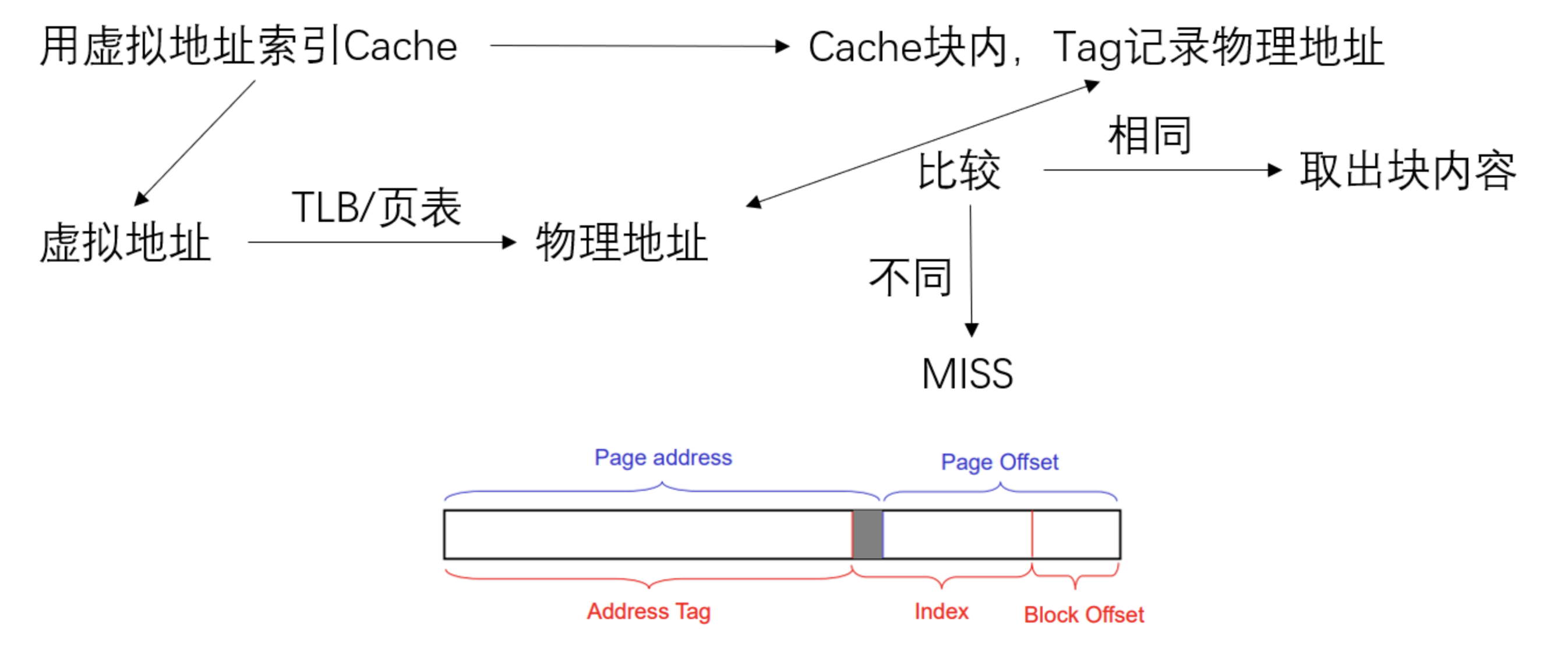

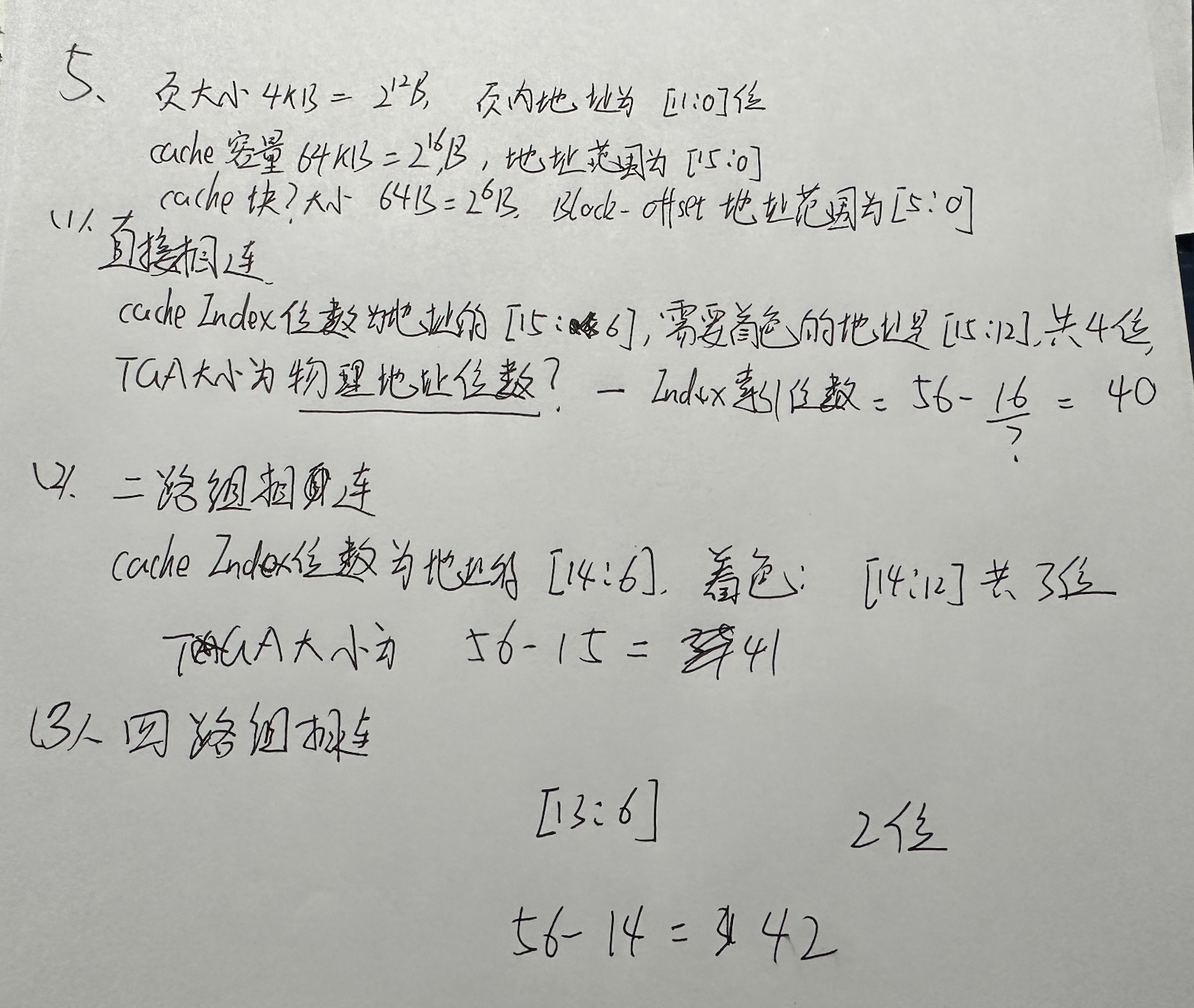

VIPT(虚index,实tag)结构中,需要在cache中使用页着色技术.vipt即用虚拟地址索引cache,用物理地址匹配tag

当vipt的cache,每一路的容量大于页的大小的时候,就会出现cache别名问题

这个同学总结的非常精辟…我就不多费时间了…

考虑如下情况:

32位机器,虚地址V1:0xe0001120 虚地址V2:0xf0002120,都映射到物理地址P: 0x00000120。

页大小4KB,占地址的低12位。于是虚拟地址和物理地址的第12位一定相同。

当Cache每路的大小不超过页大小时,用来i n d e x indexindex的地址位在[ 11 : 0 ] 之间,于是V1和V2的i n d e x indexindex相同,在Cache中索引到同一项,于是不会出现别名。 当Cache每路的大小超过页大小时,如每路容量8KB,用来i n d e x indexindex的地址位在[ 12 : 0 ]之间。而V1和V2的第13位不同,于是索引到Cache的不同行,于是出现了同一物理地址的多处备份,也即别名。

为解决别名问题,引入软件的页着色,它保证,在给虚拟地址分配物理地址时,如果两个虚拟地址映射到同一物理地址,要求两个虚拟地址的页着色位相同,即上图中对应Cache I n d e x IndexIndex与P a g e − o f f s e t Page-offsetPage−offset之间差额的灰色部分相同。

第十一章: 存储管理

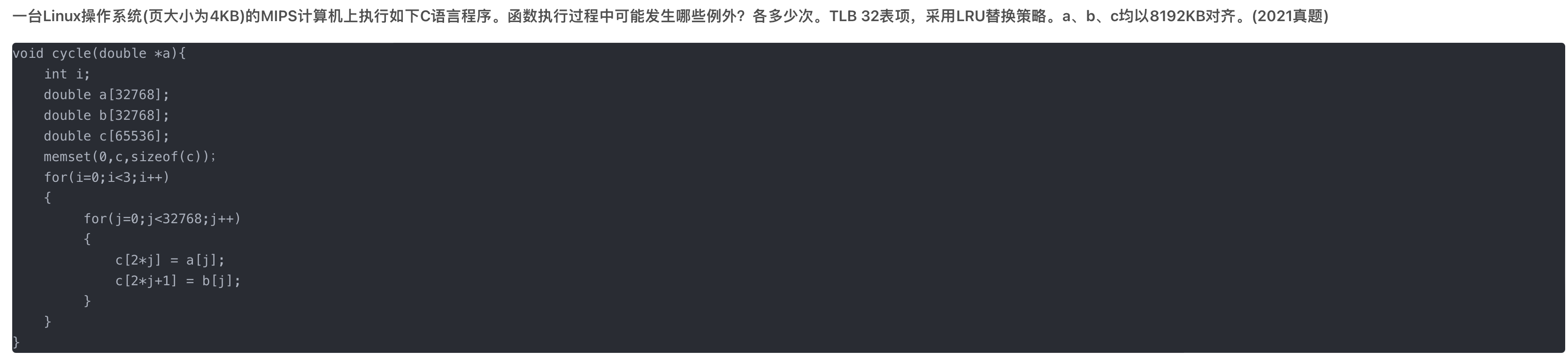

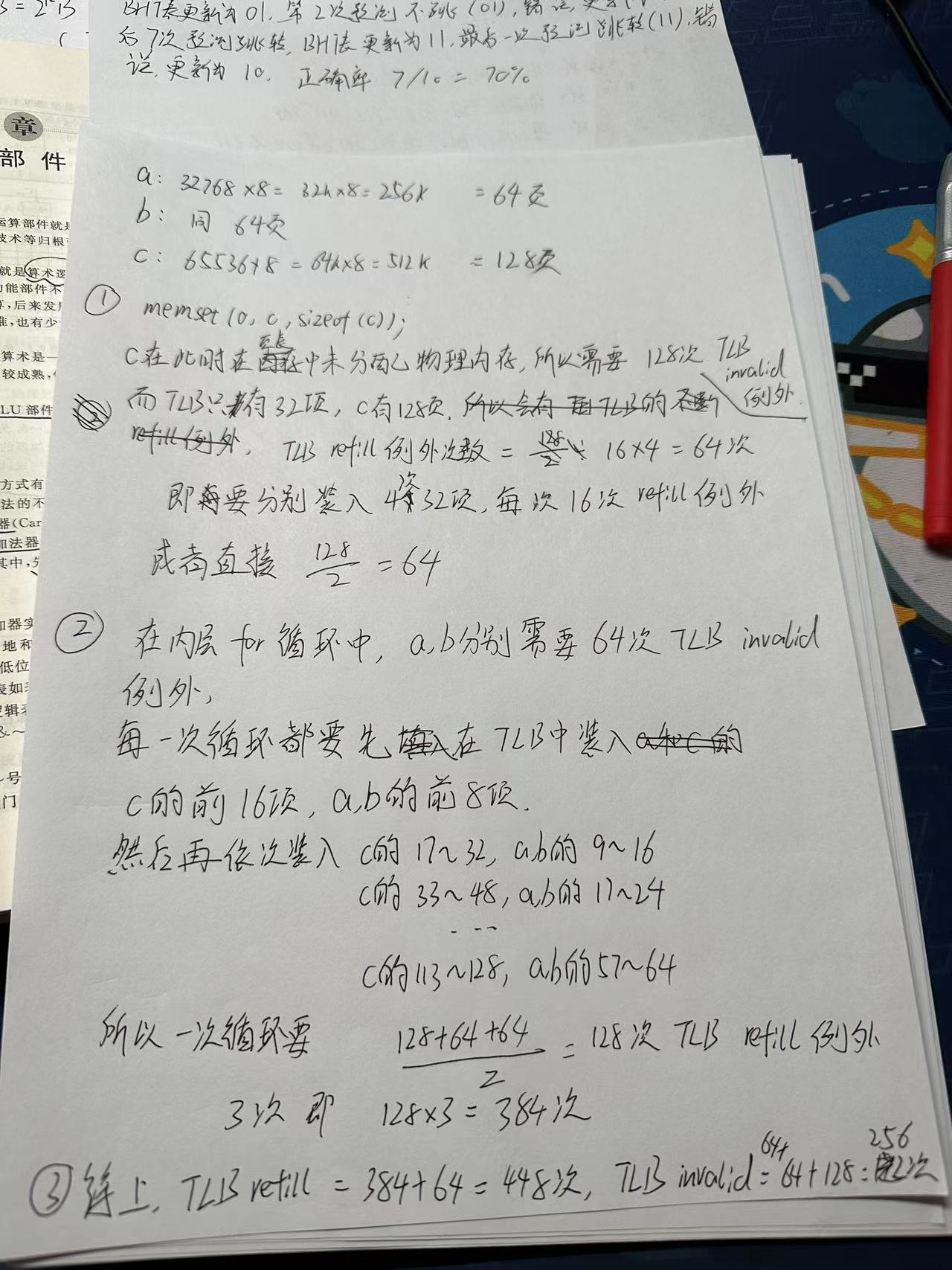

16*4 + 128

(64/2 + 64/2 ) * 3 + 64

(64/2 + 64/2 ) * 3 + 64

算的有点小问题….一个tlb项对应两个物理页才对

ab都128页

256次invalid

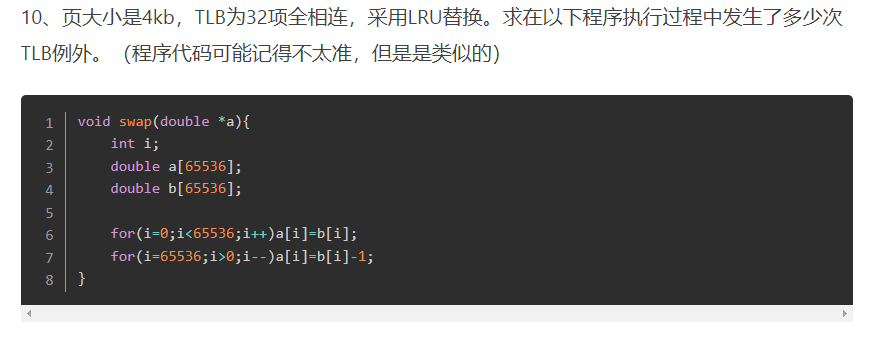

refill的话 注意看两次循环是一个从头开始,一个从尾部开始,所以最后应该要有重叠的部分!

应该是256-32

20年题目

1

五级流水: 取址,译码,执行,访存,写会 IF,ID,EX,MEM,WB 英文全称是什么呢??

指令相关: 数据相关、结构相关和控制相关

数据相关: WAW,RAW,WAR

2

注意还要除 million, 10的6次方

(1)

A:2 B:4 C:3 MIPS

(2) 都一样,因为运行时间一样

3

(1)

原码: -2的63次方+1 ~ 2的63次方-1

补码: -2的63次方 ~ 2的63次方-1

(2)

补码:1111 1111 ………………

原码:1 0000000…… 1

所以是-1

4

5

6 电路图

7 多处理器

9 转移猜测

10

128+32invalid 64+32refill来着

7788的存储

所以第十章第一题那三个如果都是32位处理器情况下tag都是31:12吗